# swissbit®

**Application Note**

**AN2107de**

NAND flash endurance testing

© Swissbit AG 2022

© Creative-Commons-Lizenz<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>Dieses Werk steht unter der Creative-Commons-Lizenz "Namensnennung 4.0 International". Um eine Kopie dieser Lizenz zu sehen, besuchen Sie http://creativecommons.org/licenses/by/4.0/

#### **Inhaltsverzeichnis**

- 1 Einleitung

- 2 Das Floating-Gate

- 3 Fowler-Nordheim-Tunneleffekt

- 4 Zell-Schädigung

- 5 Belastungstests

- 6 Zusammenfassung

#### 1 Einleitung

Typische Einsatzszenarien für NAND-Flash gehen von einer Nutzungsdauer von 3–5 Jahren aus und teilweise auch deutlich darüber hinaus. Entsprechend wird der einzusetzende Flash-Typ (SLC, pSLC, MLC, TLC, QLC) ausgewählt, der die nötige "Endurance", also die Lebensdauer gemessen in Lösch- und Programmierzyklen, aufweist. Hierbei unterstützt das "Lifetime-Monitoring-Tool", das auf dem Swissbit-FTP-Server heruntergeladen werden kann [1], um anhand der Zielapplikation den Verschleiß bzw. die benötigten TBW² über die Lebensdauer hochzurechnen.

Soll im Zuge der Qualifikation eines NAND-Flash-Speichers für ein Projekt auch die spezifizierte "Endurance" überprüft werden, so hat die Alterungsgeschwindigkeit einen erheblichen Einfluss auf das Ergebnis. Im Folgenden werden die Effekte aufgezeigt, die bei zu schnellem Altern auftreten, und es wird gezeigt, wie sie sich vermeiden lassen.

#### 2 Das Floating-Gate

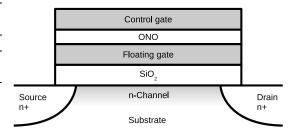

Die Abbildung 1 zeigt schematisch den Querschnitt einer NAND-Flash-Zelle. Diese Zelle entspricht dem Aufbau eines Feldeffekt-Transistors, wo zwischen dem Control-Gate und dem Substrat eine weitere leitende Lage

eingebaut wurde. Diese Lage ist von allen Seiten von Dielektrika (SiO<sub>2</sub>, ONO) umgeben. Da sie keine elektrisch leitende Verbindung besitzt, wird die Lage "Floating-Gate" genannt.

2

Trägt das Floating-Gate keine Ladung, verhält sich die NAND-Flash-Zelle wie ein Feldeffekt-Transistor: Durch das Anlegen einer positiven Spannung am Control-Gate entsteht ein elektrostatisches Feld zwischen Substrat und Control-Gate. Entsprechend konzentrieren sich freie Elektronen an der Oberseite des Substrates, und bilden einen Kanal zwischen "Source" und "Drain". Der Transistor leitet.

Trägt das Floating-Gate jedoch eine negative Ladung in Form freier Elektronen, wird das elektrische Feld kompensiert, das durch die positive Spannung am Control-Gate erzeugt wird, und es wirkt kein elektrisches Feld mehr auf die freien Ladungsträger im Substrat. Folglich bildet sich kein Kanal, und der Transistor leitet nicht.

In diesem Beispiel nimmt das Floating-Gate zwei Zustände ein: Geladen und ungeladen (neutral). Damit kann die Zelle ein Bit speichern. Bei MLC-Speicher lassen sich zwei Bits pro Zelle speichern. Entsprechend kann das Floating-Gate vier verschiedene Ladungsmengen tragen. Zum Auslesen der Information werden verschiedene Spannungen am Control-Gate angelegt.

Abbildung 1: NAND-Flash-Zelle

#### 3 Fowler-Nordheim-Tunneleffekt

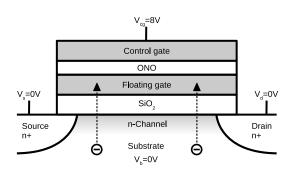

Um die Zelle zu programmieren, also Elektronen in das Floating-Gate einzubringen,

<sup>&</sup>lt;sup>2</sup>"Terabytes written" – Die Mindest-Datenmenge, die bei einem standardisierten Test auf eine SSD geschrieben werden kann

## swissbit<sup>®</sup>

muss die Siliziumoxid-Isolationsschicht überwunden werden. Hier kommt der "Fowler-Nordheim-Tunneleffekt" zum Anwendung: Durch Anlegen eines starken elektrostatischen Feldes zwischen Substrat und Control-Gates können Elektronen die Potentialbarriere des Isolationsmaterials durchtunneln. Dies ist ein quantenmechanischer Effekt, der es den Elektronen ermöglicht, eine Potentialbarriere zu überwinden bzw. zu durchtunneln, die höher ist als die Energie der Elektronen.

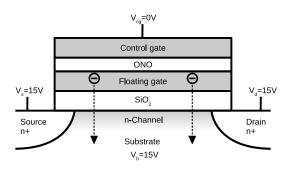

Um die Information in der Zelle wieder zu löschen, also die Elektronen zu entfernen, kommt das gleiche Vorgehen zur Anwendung, allerdings mit umgekehrter Polarität. Da hierbei an das Substrat eine positive Spannung angelegt wird, werden alle Zellen in der Umgebung beeinflusst. Dies ist der Grund, weshalb nur ganze Flash-Blöcke zusammen gelöscht werden können, während die Programmierung feingranularer erfolgen kann.

Abbildung 2 zeigt den Programmiervorgang mittels Fowler-Nordheim-Tunneleffekt und Abbildung 3 den entsprechenden Löschvorgang. Wird mehr als ein Bit pro Zelle gespeichert (bei MLC, TLC, QLC), müssen mehr als zweiverschiedene Potentiale erreicht werden. Dazu wird das elektrische Feld mehrfach mit kurzen Pulsen angelegt. Nach jedem Puls folgt ein Auslesen des erreichten Potentials. Ist die benötigte Anzahl von Elektronen im Floating-Gate erreicht, stoppt der Programmiervorgang.

Abbildung 2: Programmiervorgang

Abbildung 3: Löschvorgang

#### 4 Zell-Schädigung

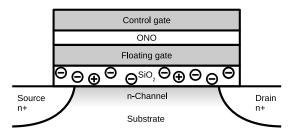

Durch die Programmier- und Löschoperationen wird das Tunnel-Oxid dauerhaft geschädigt. Man spricht hier vom sogenannten "Wear-Out". Atomare Bindungen im Oxid und an der Grenzfläche des Substrates werden aufgebrochen, es kommt so sogenannten "Defekten". Dadurch werden Energiezustände (Störstellen) geschaffen, die von Elektronen oder Löchern besetzt werden können (sogenannte "traps"). Diese Defekte schwächen die Potentialbarriere. Die Wahrscheinlichkeit, dass ein Elektron in einer gewissen Zeit aus dem Floating-Gate entkommen kann, steigt. Man spricht hier vom "trap assisted tunneling" (TAT). Dieser ist die Ursache des "stress induced leakage current" (SILC), also einem durch Beanspruchung ausgelösten Leckstrom. Der damit verbundene Ladungsverlust im Floating-Gate ist die Ursache für die exponentielle Abnahme der "Data-Retention-Time" über die Anzahl der Programmier- und Löschzyklen. Die Data-Retention-Time bezeichnet den Zeitraum, über den der Flash, die gespeicherten Informationen halten kann, ohne dass die Information durch Umkopieren aufgefrischt werden muss. Typischerweise wird die Endurance so spezifiziert, dass der Flash die Daten mindestens 10 Jahre bis zu einem Wear-Out von 10 % der zulässigen Programmier- und Löschzyklen halten kann sowie 1Jahr bei der maximalen Anzahl an Zyklen.

Die Defekte im Siliziumoxid werden aber nicht nur von Elektronen aus dem Floating-Gate besetzt, die ungewollt abfließen, son-

grammieren und Löschen durch das Oxid tunneln. Dabei zeigt die Anzahl der Elektronen, die an einer Störstelle haften bleiben, eine Quadratwurzel-Abhängigkeit von der Anzahl der Programmier- und Löschzyklen, während das Ablösen ("Detrapping") von einer Störstelle mit einer logarithmischen Abhängigkeit (In) der Zeit geschieht und bei erhöhter Temperatur stark beschleunigt wird [2].

Abbildung 4 zeigt Ladungsträger, die Aufgrund einer großen Anzahl an Programmierund Löschzyklen in kurzer Zeit an Störstellen haften blieben. Diese Ansammlung von überwiegend negativen Ladungen erhöht zum Einem die Schwellwert-Spannung, die am Control-Gate angelegt werden muss, damit sich ein Kanal bildet. Dadurch können ab einem gewissen Level die Zustände der Floating-Gates nicht mehr eindeutig bestimmt werden. Dies betrifft besonders den gelöschten Zustand. Zum anderen führt das Detrapping zu einer Verringerung der Schwellwert-Spannung, wodurch sich ebenfalls die Zustände nicht mehr identifizieren lassen und die gespeicherten Daten verloren gehen. Zudem ist der Stress für das Tunnel-Oxid beim Löschen umso größer, je mehr negative Ladungen im Oxid gefangen sind.

Abbildung 4: Ladungsträger im Tunnel-Oxid

## 5 Belastungstests

Soll im Zuge der Qualifikation eines NAND-Flash-Speichers die spezifizierte Haltbarkeit überprüft werden, muss sichergestellt werden,

dern auch von den Elektronen, die beim Pro- tronen im Tunnel-Oxid. Gemäß JEDEC JESD22-A117 [3] ist bei Tests zur Haltbarkeit unbedingt darauf zu achten, unrealistischen Stress zu vermeiden, wie er auftreten würde, wenn der Test die spezifizierte Lebensdauer des Speichers in wenigen Tagen erreichen würde.

> Bei Belastungstests muss daher der Flash ausreichend Zeit zur Erholung haben. Dies kann entweder durch regelmäßige Pausen, eine geringere Schreibgeschwindigkeit oder erhöhte Flash-Temperatur erfolgen. Während Flash am Anfang seiner Lebenszeit noch relativ unempfindlich auf eine schnelle Folge von Programmier- und Löschzyklen reagiert, nimmt die Empfindlichkeit mit zunehmenden Defekten im Tunnel-Oxid deutlich zu [4].

> Ist ein schnelles Testen nötig, so ist es mit allen aktuellen Flash-Technologien möglich, den Speicher bei +85°C innerhalb von 1000 Stunden auf die spezifizierte Anzahl von Programmier- Löschzyklen zu altern. Dabei muss lediglich beachtet werden, alle Flash-Blöcke mit annähernd gleicher Geschwindigkeit zu altern, was am besten durch sequentielles Schreiben über den gesamten Adressraum erfolgt. Kann der Host nicht bei dieser Temperatur betrieben werden, oder kann das Speichermedium nicht abgesetzt in einem Ofen betrieben werden, so genügt es auch, die Flash-Komponenten - z.B. mit einer Heizzange entsprechend zu erhitzen. Hierbei ist zu beachten, dass die Data-Retention-Time am Ende der Lebensdauer bei +85°C nur noch wenige Tage beträgt. Sowie der Schreibtest beendet ist, sollte daher die Temperatur reduziert werden.

## 6 Zusammenfassung

Die Schädigung der Speicherzellen von Flash-Speichern hängt sowohl von der Anzahl der erfolgten Programmier- und Löschzyklen ab als auch von der Geschwindigkeit, mit der diese Zyklen erfolgen. Bei der typischen Lebens- bzw. Einsatzdauer eines Flash-Speichermediums sind die Zyklen überwiegend gleichmäßig über einen Zeitraum von mindestens drei Jahren dass es nicht zu einem Frühausfall des Spei- verteilt. Der Zeitraum zwischen zwei Zyklen ist chers kommt durch die Ansammlung von Elek- dann ausreichend für den Abbau der Ladun-

gen im Tunnel-Oxid, und der Flash erreicht seine spezifizierte Anzahl an Zyklen. Bei einer untypisch kurzen Zykluszeit (insbesondere bei Qualifikationstests), muss zwischen den Zyklen ausreichend Zeit für die Erholung der Zellen gegeben sein und/oder die Temperatur erhöht werden, um die spezifizierte Lebensdauer zu erreichen.

Die Swissbit AG unterstützt Sie gerne bei der Wahl geeigneter Testmethoden.

#### Literatur

- [1] ftp://public:public@ftp.swissbit.com/ SFxx\_LTM\_Tool/

- [2] Mielke, N.; Belgal, H.; Kalastirsky, I. et al. Flash EEPROM threshold instabilities due to charge trapping during program-/erase cycling; IEEE Transactions on Device and Materials Reliability, vol. 4, no. 3, pp. 335–343, 2004.

- [3] JEDEC Standard JESD22-A117C. Electrically Erasable Programmable ROM (EEPROM) Program/Erase Endurance and Data Retention Stress Test; Technical Report; JEDEC Solid State Technology Association: Arlington, VA, USA, 2011.

- [4] Spinelli, A.; Compagnoni, C.; Lacaita, A. Reliability of NAND Flash Memories: Planar Cells and Emerging Issues in 3D Devices. Computers 2017, 6, 16, doi:10.3390/computers6020016.

## Kontaktieren Sie uns

| Hauptsitz             | <b>Swissbit AG</b> Industriestraße 4 9552 Bronschhofen Schweiz                                                        | Tel. +41 71 913 03 03 sales@swissbit.com         |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Deutschland (Berlin)  | Swissbit Germany AG<br>Bitterfelder Straße 22<br>12681 Berlin<br>Deutschland                                          | Tel. +49 30 936 954 0<br>sales@swissbit.com      |

| Deutschland (München) | Swissbit Germany AG<br>Leuchtenbergring 3<br>81677 München<br>Deutschland                                             | Tel. +49 30 936 954 400<br>sales@swissbit.com    |

| Nord- und Südamerika  | Swissbit NA Inc.<br>238 Littleton Road, Suite 202B<br>Westford, MA 01886<br>USA                                       | Tel. +1 978-490-3252<br>salesna@swissbit.com     |

| Japan                 | Swissbit Japan Co., Ltd.<br>CONCIERIA Tower West 2F<br>6-20-7 Nishishinjuku<br>Shinjuku City, Tokyo 160-0023<br>Japan | Tel. +81 3 6258 0521<br>sales-japan@swissbit.com |

| Taiwan                | Swissbit Taiwan<br>3F., No. 501, Sec.2, Tiding Blvd.<br>Neihu District, Taipei City 114<br>Taiwan, R.O.C.             | Tel. +886 912 059 197<br>salesasia@swissbit.com  |

| China                 | Swissbit China                                                                                                        | Tel. +886 958 922 333<br>salesasia@swissbit.com  |

#### Disclaimer:

The information in this document is subject to change without notice. Swissbit AG ("SWISSBIT") assumes no responsibility for any errors or omissions that may appear in this document, and disclaims responsibility for any consequences resulting from the use of the information set forth herein. SWISSBIT makes no commitments to update or to keep current information contained in this document. The products listed in this document are not suitable for use in applications such as, but not limited to, aircraft control systems, aerospace equipment, submarine cables, nuclear reactor control systems and life support systems. Moreover, SWISSBIT does not recommend or approve the use of any of its products in life support devices or systems or in any application where failure could result in injury or death. If a customer wishes to use SWISSBIT products in applications not intended by SWISSBIT, said customer must contact an authorized SWISSBIT representative to determine SWISSBIT willingness to support a given application. The information set forth in this document does not convey any license under the copyrights, patent rights, trademarks or other intellectual property rights claimed and owned by SWISSBIT.

ALL PRODUCTS SOLD BY SWISSBIT ARE COVERED BY THE PROVISIONS APPEARING IN SWISSBIT'S TERMS AND CONDITIONS OF SALE ONLY, INCLUDING THE LIMITATIONS OF LIABILITY, WARRANTY AND INFRINGEMENT PROVISIONS. SWISSBIT MAKES NO WARRANTIES OF ANY KIND, EXPRESS, STATUTORY, IMPLIED OR OTHERWISE, REGARDING INFORMATION SET FORTH HEREIN OR REGARDING THE FREEDOM OF THE DESCRIBED PRODUCTS FROM INTELLECTUAL PROPERTY INFRINGEMENT, AND EXPRESSLY DISCLAIMS ANY SUCH WARRANTIES INCLUDING WITHOUT LIMITATION ANY EXPRESS, STATUTORY OR IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE.

© 2022 SWISSBIT AG